Unit 9, 12 Mars Rd

Tel: +61 2 9420 0690

Lane Cove NSW 2066

Fax: +61 2 9420 0692

Australia

www.cap-xx.com

CAP-XX (Australia) Ptv Ltd ABN 28 077 060 872 ACN 077 060 872

# HS103 / HS203 SUPERCAPACITOR Datasheet Rev 4.3, July 2018

This Datasheet should be read in conjunction with the CAP-XX Supercapacitors Product Guide which contains information common to our product lines.

## **Electrical Specifications**

The HS103 is a single cell supercapacitor. The HS203 is a dual cell supercapacitor with two HS103 cells in series, so HS203 capacitance = Capacitance of HS103/2 and HS203 ESR =  $2 \times HS103 ESR$ .

#### **Table 1: Absolute Maximum Ratings**

| Parameter   | Name  |       | Conditions | Min | Typical | Max | Units |

|-------------|-------|-------|------------|-----|---------|-----|-------|

| Terminal    | Vpeak | HS103 |            | 0   |         | 2.9 | V     |

| Voltage     |       | HS203 |            |     |         | 5.8 |       |

| Temperature | Tmax  |       |            | -40 |         | +85 | °C    |

| Parameter                 | Name             |       | Conditions         | Min | Typical | Max  | Units |

|---------------------------|------------------|-------|--------------------|-----|---------|------|-------|

| Terminal<br>Voltage       | Vn               | HS103 |                    | 0   |         | 2.75 | V     |

|                           |                  | HS203 |                    | 0   |         | 5.5  |       |

| Capacitance               | С                | HS103 | DC, 23°C           | 400 | 500     | 600  | - mF  |

|                           |                  | HS203 |                    | 200 | 250     | 300  |       |

| EGD                       | ESR              | HS103 | DC, 23°C           |     | 30      | 36   | mΩ    |

| ESR                       |                  | HS203 |                    |     | 55      | 66   |       |

| Leakage<br>Current        | $I_L$            |       | 2.75V, 23°C 120hrs |     | 1       | 2    | μA    |

| RMS Current               | I <sub>RMS</sub> |       | 23°C               |     |         | 6    | А     |

| Peak Current <sup>1</sup> | IP               |       | 23°C               |     |         | 30   | А     |

#### **Table 2: Electrical Characteristics**

<sup>1</sup>Non-repetitive current, single pulse to discharge fully charged supercapacitor.

#### **Table 3: Thickness**

| HS103F | 1.0mm | No adhesive tape on underside of the supercapacitor | HS103G |       | Adhesive tape on underside, release tape removed |

|--------|-------|-----------------------------------------------------|--------|-------|--------------------------------------------------|

| HS203F | 2.1mm |                                                     | HS203G | 2.2mm |                                                  |

## **Definition of Terms**

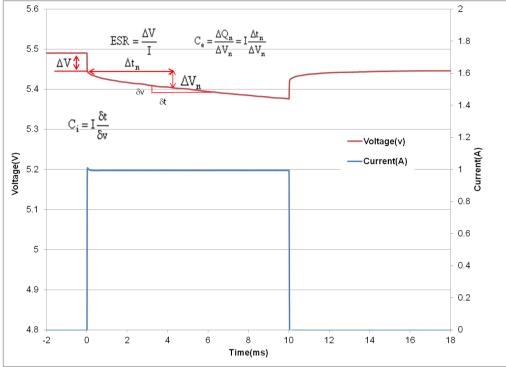

In its simplest form, the Equivalent Series Resistance (ESR) of a capacitor is the real part of the complex impedance. In the time domain, it can be found by applying a step discharge current to a charged cell as in Fig. 1. In this figure, the supercapacitor is pre-charged and then discharged with a current pulse, I = 1A for duration 0.01 sec.

Figure 1: Effective capacitance, instantaneous capacitance and ESR for an HS203

The ESR is found by dividing the instantaneous voltage step ( $\Delta V$ ) by I. In this example = (5.49V - 5.45V)/1A = 40m\Omega.

The instantaneous capacitance  $(C_i)$  can be found by taking the inverse of the derivative of the voltage, and multiplying it by I.

The effective capacitance for a pulse of duration  $\Delta t_n$ , Ce( $\Delta t_n$ ) is found by dividing the total charge removed from the capacitor ( $\Delta Q_n$ ) by the voltage lost by the capacitor ( $\Delta V_n$ ). For constant current Ce( $\Delta t_n$ ) = I x  $\Delta t_n/\Delta V_n$ . Ce increases as the pulse width increases and tends to the DC capacitance value as the pulse width becomes very long (~10 secs). After 2msecs, Fig 1 shows the voltage drop V<sub>2ms</sub> = (5.45 V - 5.416V) = 34mV. Therefore Ce(2ms) = 1A x 2ms/34mV = 58.8mF. After 10ms, the voltage drop = 5.45 V - 5.376V = 74mV. Therefore Ce(10ms) = 1 A x 10ms/74mV = 135mF. The DC capacitance of an HS203 = 0.25 F. Note that  $\Delta V$ , or IR drop, is not included because very little charge is removed from the capacitor during this time. Ce shows the time response of the capacitor and it is useful for predicting circuit behavior in pulsed applications.

# **Measurement of DC Capacitance**

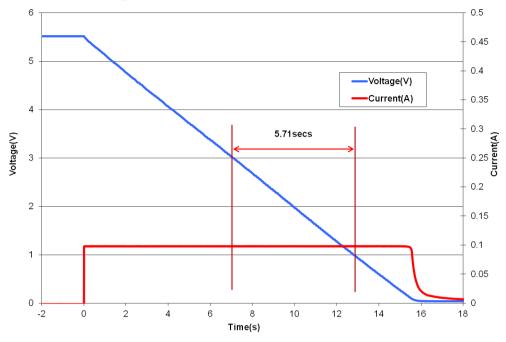

Fig 2 shows the measurement of DC capacitance by drawing a constant 100mA current from a fully charged supercapacitor and measuring the time taken to discharge from 1.5V to 0.5V for a single cell, or from 3V to 1V for a dual cell supercapacitor. In this case,  $C = 0.1A \times 5.71s / 2V = 285.5mF$ , which is well within the 0.25F +/- 20% tolerance for an HS203 cell.

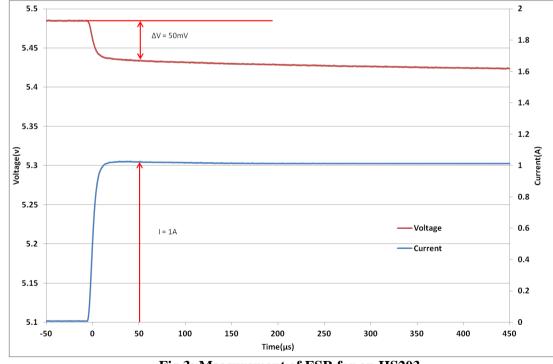

#### **Measurement of ESR**

Fig 3 shows DC measurement of ESR by applying a step load current to the supercapacitor and measuring the resulting voltage drop. CAP-XX waits for a delay of 50 $\mu$ s after the step current is applied to ensure the voltage and current have settled. In this case the ESR is measured as 50mV/1.A = 50m $\Omega$ .

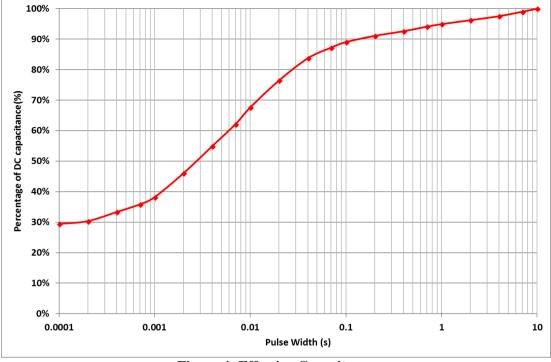

## **Effective Capacitance**

Fig 4 shows the effective capacitance for the HS103, HS203 @ 23°C. This shows that for a 1ms PW, you will measure 38% of DC capacitance or 190mF for an HS103 or 95mF for an HS203. At 10ms you will measure 67% of the DC capacitance, and at 100ms you will measure 89% of DC capacitance. Ceffective is a time domain representation of the supercapacitor's frequency response. If, for example, you were calculating the voltage drop if the supercapacitor was supporting 1A for 10ms, then you would use the Ceff(10ms) = 67% of DC capacitance = 167.5mF for an HS203, so Vdrop = 1A x ESR + 1A x duration/C = 1A x 55mQ + 1A x 10ms / 167.5mF = 115mV. The next section on pulse response shows how the effective capacitance is sufficient for even short pulse widths.

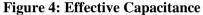

### **Pulse Response**

Fig 5 shows that the HS203 supercapacitor does an excellent job supporting a GPRS class 10 pulse train, drawing 1.8A for 1.1ms at 25% duty cycle. The source is current limited to 0.6A and the supercapacitor provides the 1.2A difference to achieve the peak current. At first glance the freq response of Fig 8 indicates the supercapacacitor would not support a 1ms pulse, but the Ceff of 43.8mF coupled with the low ESR supports this pulse train with only ~100mV droop in the supply rail.

Fig 5: HS203 Pulse Response with GPRS Class 10 Pulse Train

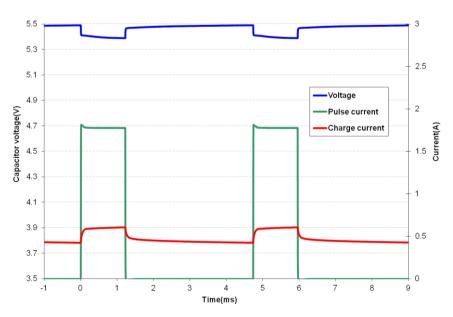

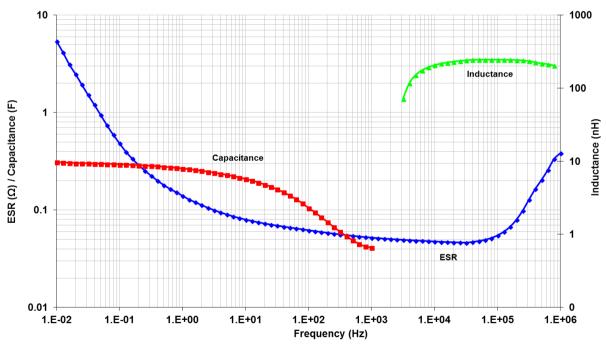

## **DC** Capacitance variation with temperature

Fig 6 shows that DC capacitance is approximately constant with temperature.

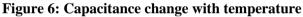

# ESR variation with temperature

**Figure 7: ESR change with temperature**

Fig 7 shows that ESR at -40°C is ~2.1x ESR at room temp, and that ESR at 70°C is ~0.8 x ESR at room temperature.

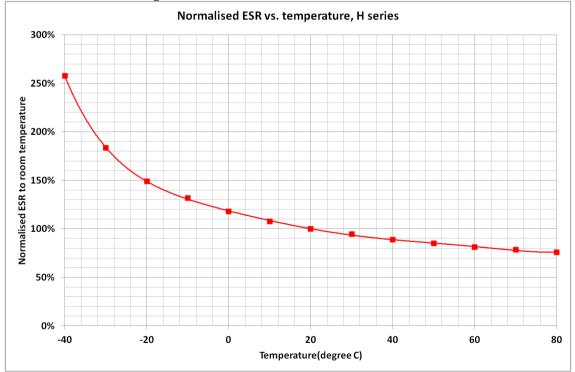

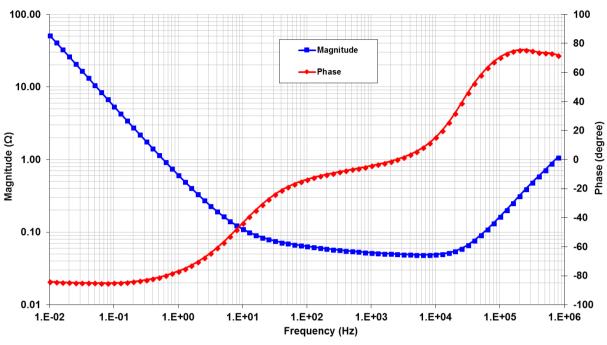

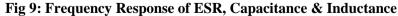

# **Frequency Response**

HS203 Magnitude and Phase vs. Frequency

Fig 8: Frequency Response of Impedance (biased at 5.5V with a 50mV test signal)

HS203 ESR, Capacitance and Inductance vs. Frequency

Fig 8 shows the supercapacitor behaves as an ideal capacitor until approx 9 Hz when the magnitude no longer rolls off proportionally to 1/freq and the phase crosses -45°. Performance of supercapacitors with frequency is complex and the best predictor of performance is Fig 4 showing effective capacitance as a function of pulsewidth.

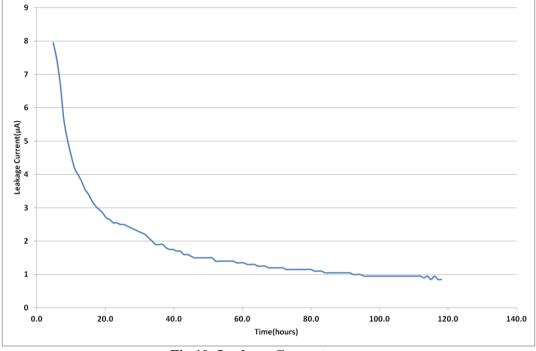

# Leakage Current

Fig 10: Leakage Current

Fig 10 shows the leakage current for HS103 at room temperature. The leakage current decays over time, and the equilibrium value leakage current will be reached after ~120hrs at room temperature. The typical equilibrium leakage current is  $1\mu$ A at room temperature. At 70°C leakage current will be ~5 $\mu$ A.

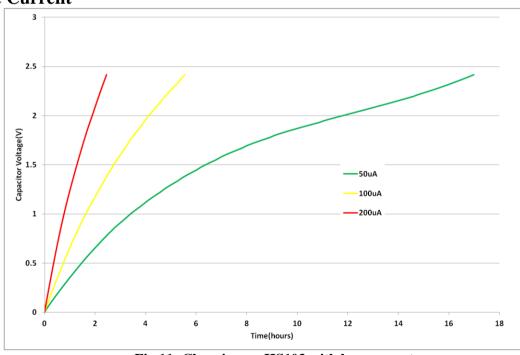

The corollary to the slow decay in leakage currents shown in Fig 10 is that charging a supercapacitor at very low currents takes longer than theory predicts. At higher charge currents, the charge rate is as theory predicts. For example, it should take  $0.5F \times 2.4V / 0.00005A = 6.7hrs$  to charge a 0.5 F supercapacitor to 2.4V at  $50\mu A$ , but Fig 11 shows it took 17hrs. At  $200\mu A$  charging occurs at a rate close to the theoretical rate.

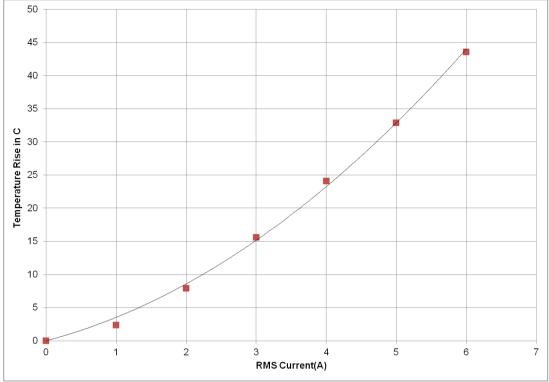

# **RMS Current**

Continuous current flow into/out of the supercap will cause self heating, which limits the maximum continuous current the supercapacitor can handle. This is measured by a current square wave with 50% duty cycle, charging the supercapacitor to rated voltage at a constant current, then discharging the supercapacitor to half rated voltage at the same constant current value. For a square wave with 50% duty cycle, the RMS current is the same as the current amplitude. Fig 12 shows the increase in temperature as a function of RMS current. From this, the maximum RMS current in an application can be calculated, for example, if the ambient temperature is 40°C, and the maximum desired temperature for the supercapacitor is 70°C, then the maximum RMS current should be limited to 4.5A, which causes a 30°C temperature increase.

# **CAP-XX Supercapacitors Product Guide**

Refer to the package drawings in the CAP-XX Supercapacitors Product Guide for detailed information of the product's dimensions, PCB landing placements, active areas and electrical connections.

Refer to the CAP-XX Supercapacitors Product Guide for information on endurance and shelf life, transportation and storage, assembly and soldering, safety and RoHS/EREACH certification.